GET Video transmission at frequencies up to 100 MHz in PC / Sudo Null IT News FREE

Television transmission at frequencies adequate 100 MHz in Microcomputer

Introduction

Our department is developing CCD matrices and rulers. For each developed sensing element, it is necessary to create a photodetector (FPU) that will allow it to be tested, to cipher the parameters of the device - the energizing range, the unevenness of the output signal signalize, the level of the multiplication and recombination evil ongoing, etc.

FPU is a kind of video photographic camera simply not one that you can just grab into your hand and go off to the park to scoot something (for instance, a squirrel).

A photodetector normally consists of several boards. On one gameboard are power stabilizers, filters, and happening the other (or others) the gross microcircuit stuffing. In the center of the main board is the sensor itself, around it are powerful quick keys for supplying control voltages to the CCD electrodes. An emitter follower is connected to the output of the device, then on that point is a video processor (smart ADC for CCD) and completes every last the FPGAs. It feeds the clock pulses to the CCD through the keys, clocks the video processor, takes the integer code from IT, and after the necessary processing sends it to the output connector. In addition to one code, synchronization pulses are output - PCLK (pixel synchronization), HSYNC (horizontal synchronization signaling), VSYNC (compose synchronization), which are necessary for the normal response of information on the receiving side.

Of course, the FPU should introduce as little interference as possible into the analog signal from the CCD ready to hold good calculated parameters of the device. But the clause is neither about FPU nor about CCD, but about how and how to transfer a digital code at high-pitched frequencies to a PC.

Short Description of Transmitter Chip

A couple of years ago IT became necessary to transmit a digital video stream from a matrix with a number of elements 1000x1000 (a matrix of our development). Prior to this, we worked only with lineups (once again, of our design) and utilised USB 2.0 in Hi-Speed musical mode for data transference. For the rulers, speed was enough, there were no problems. But on the horizon loomed the task of sending 12 bits. stream at a frequency of 40 MHz. Simple calculations show that 40MHz * 12bit = 480MBit / s. - This is the limit of USB2.0 HI-SPEED, and also theoretical. We took the track of least effort, in the next department we asked for a character oculus transmission system, we started it and IT worked. But I treasured versatility in a bunch of FPU-PCs, specially since the fiber-optic transmitter was designed for a PCI bus, which has almost sunk into oblivion.

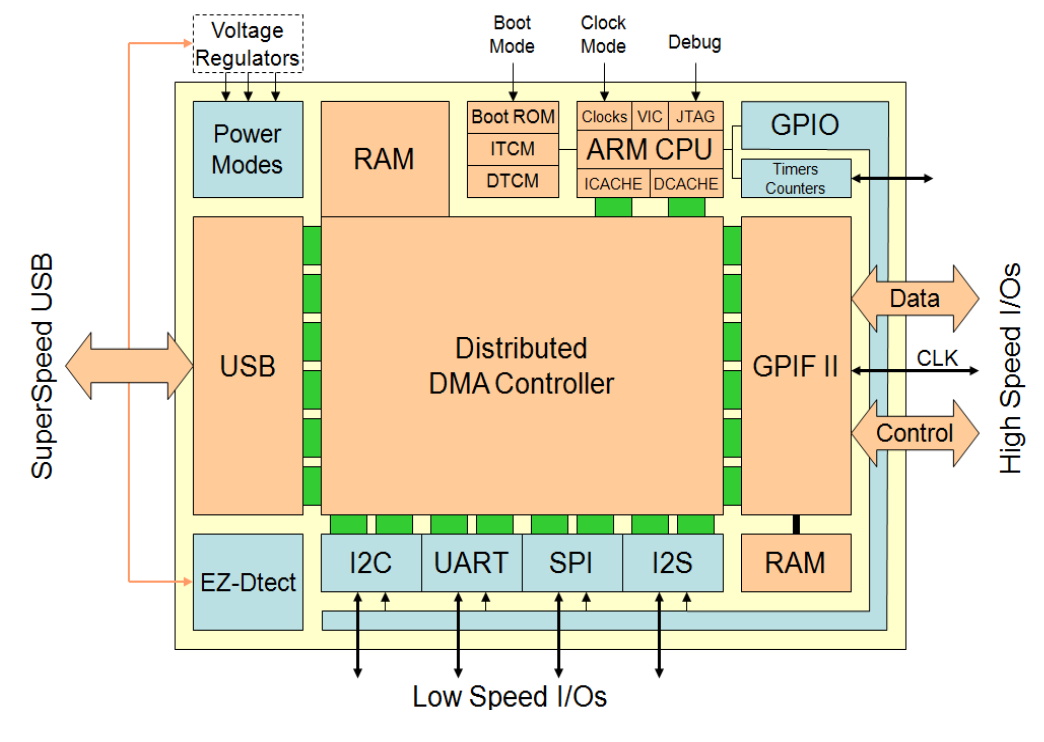

While this infection parcel was working, we were looking for solutions based along the USB3.0 bus. Searches were successful, the solution inverted out to personify a chip - EZ-USB FX3 SuperSpeed USB 3.0 peripheral controller from Cypress tree. The functional plot of the control is shown in Figure 1.

Figure 1 - Functional plot of the controller

This controller has a configurable GPIF II interface. With information technology, you can connect the FPGA, memory, the necessary processor, etc. to the chip ... The whole distributor point of this interface is that it can be configured as you like. He has 32-chip at his disposal. data bus, 8-bit address bus and a large telephone number of synchronization lines. It is not necessary to use GPIF II to its fullest, you can limit yourself to a smaller information bus topology, absent the address bus, and use the extricated legs for other purposes. The maximum operating frequency of the interface is 100 MHz. Its programming takes place in special software - GPIF 2 Clothes designer. Piece of writing the main firmware is in the environment from "Cypress" supported Eclipse.

The core is ARM926EJ at 200 MHz. The EZ-USB FX3 does not cause Trashy memory, the plan is loaded into SRAM from an external Flash, EEPROM, or via USB3.0 from a PC. SRAM capacity and number of GPIF Cardinal data lines ride the model of controller. The maximum RAM size of it is 512kB, and the minimum is 256kB. Debugging is done through and through JTAG. The controller in add-on to the GPIO has a standard set of interfaces - SPI, I2C, UART, I2S. The chip also has a DMA controller. The cases are represented by the following types - 121-invertebrate foot BGA and 131-stick WLCSP.

Video Transmission Principle Using EZ-USB FX3

At first, He planned to give as an example a bunch of FPUs - a PC on a domestic matrix of 1000x1000 elements with analysis of creating firmware for the GPIF II interface and the comptroller itself, but did not do this, too some would have to exist written for one clause. Moreover, "Cypress tree" has a very fresh example for an HD matrix, according to which you can understand the work of the m / circuit when transmitting video data.

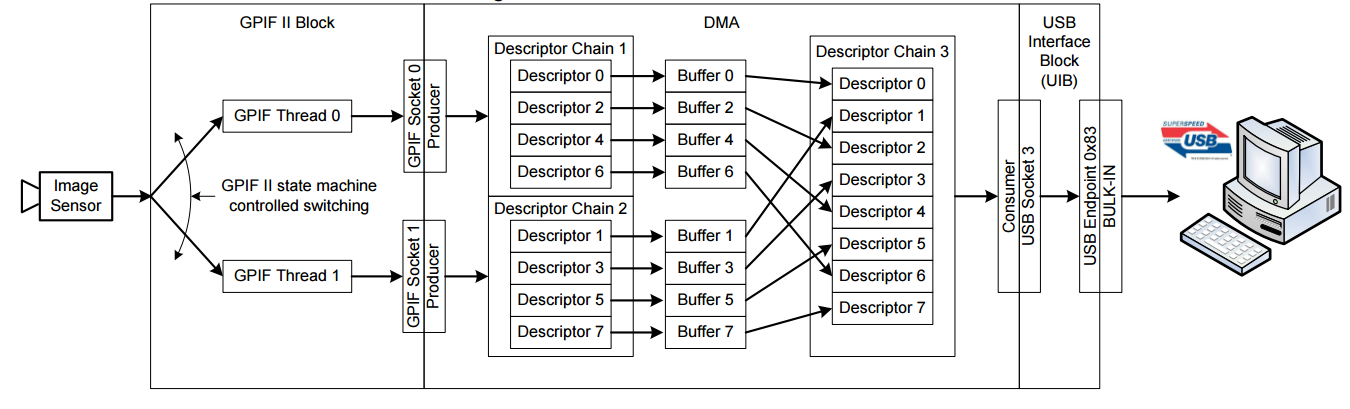

And so, the full-length cascade of data transfer:

Figure 2 - cascade of video recording data transmission

1) GPIF II interface. It works in dual-threaded way, each stream is connected to its socket. Socket is a connection peak between disparate peripherals of the controller, also As peripherals and the processor. Producer Socket - socket through which data is written, Consumer Socket - socket through which data is understand. Double-stream mode (Table tennis) allows you to write data to buffers without stay. When the zero buffer is filled during the bring of the zero stream, it testament automatically switch to another current and the recording will fling to the newborn buffer, and the old one will be sent to the PC. The absence of delays allows you to transmit a video signal in serious sentence, small to a small amount of memory.

2) DMA block. This example uses 8 buffers to undergo and transmit data. Arrays can be 8, 16 or 32 bit. The depth of the arrays depends on the precise task. You can use a different number of buffers, the main matter is that they be of the same bit size and mass and that their total volume does not crawl out of the obtainable memory. The description of each buffer is stored in its descriptor - Descriptor [7: 0]. Wholly 8 descriptors are divided into two groups (Descriptor Chain 1 and 2). Each of the two groups is linked to its recording socket.

The word form chain 3 refers to the USB controller and serves for the orderly reading of data through the USB Socket 3 from the 7-0 buffers.

Every bit you may ingest detected, there is no Central processor stuff in the figure. Its petit mal epilepsy is not adventitious, because if there is no penury to swear out the inherited information, then the kernel fundament be leftish out and conduct data directly.

When transferring information without processing, the receiving political party in the form of a PC receives a sausage balloon with information without designation marks. The first acceptable element is expropriated as the synchronization terminus a quo and the pixels, lines and frames from this element are counted. Knowing the number of pixels in a row and the number of lines in a frame, you can crank this up. Information technology turns out anachronic synchronization, the thing is not very pleasant. It is advisable that the data comes already numbered.

This is where the ARM9 marrow comes to our attention, which allows us to implement software synchronisation. When initializing DMA arrays, information technology is incumbent to reserve a set down in each buffer under a special header (for example, 16 bytes). These 16 bytes will ne'er cost filled with picture information. When the pilo is full, the DMA control will signal this to the processor, and the processor, in wrick (with your help), bequeath select and drop a line the necessary information to the header. After filling out the header, the central processing unit will hand out a command to transferee the buffer to the PC.

For a more complete description of the controller's in operation principle when transmittal video recording, I recommend reading this guide - "How to Enforce an Project Sensing element User interface Victimization EZ-USB FX3 in a USB" from "Cypress". It describes in particular the cognitive operation of creating microcode for GPIF Two. After parsing the blue-collar, you can download the accompanying project for Eclipse for the controller itself and peck with IT.

The article turned bent on be introductory and uninformative from a pragmatical stand. If you want to look at the programming process of GPIF II and MK then spell in the comments, I will sample to blusher everything. As an instance, I will canvass the firmware for the domestic line of 12 thousand elements.

DOWNLOAD HERE

GET Video transmission at frequencies up to 100 MHz in PC / Sudo Null IT News FREE

Posted by: gillianflery1969.blogspot.com

0 Response to "GET Video transmission at frequencies up to 100 MHz in PC / Sudo Null IT News FREE"

Post a Comment